Эта заметка представляет первую часть статьи, из запланированных трёх, посвящённой краткому описанию архитектуры и особенностей МК STM32F407 и его ядра — Cortex®-M4F. Её целью является показать широту возможностей, предоставляемых рассматриваемыми МК, а так же сделать дальнейшее их изучение более осмысленным, систематизированным и планомерным. Представленные описания носят, по большей части, ознакомительный характер, и нацелены на создание общего представления. По мере написания цикла заметок, многое из затронутого в ней, предполагается описать более детально, дополнив примерами практического применения. Поэтому, при первом прочтении, не следует заостряться на тем местах, которые покажутся непонятными. К их рассмотрению, возможно, стоит вернуться позже, когда будет рассматриваться соответствующая практика.

Содержание

Часть I

- Структурная схема МК

- Ядро Cortex-M4F

- Архитектура набора команд

- Центральное процессорное устройство

- Контроллер вложенных векторизованных прерываний

- Системный таймер

- Контроллер пробуждающих прерываний

- Модуль защиты памяти

- Цифровой сигнальный процессор

- Математический сопроцессор

- Системный контрольный блок

- Матрица шин

- Идентификационные регистры

-

Система отладки

- Порт отладки SWJ-DP

- Порт доступа AHB-AP

- Таблица ПЗУ

- Отладочные регистры в системном контрольном пространстве

- Модуль точек останова и подмены

- Модуль точек наблюдения и трассировки данных

- Инструментальная макроячейка трассировки

- Встроенная макроячейка трассировки

- Интерфейс порта трассировки

- Отладочный компонент микроконтроллера

Структурная схема МК

Структурная схема МК серии STM32F40XXX показана на рис.5 подраздела 2.2 ДШ и на рис. 1 этой статьи.

Функционально, изображённое на рис.1 можно разделить на три части:

- Ядро МК.

- Компоненты системы отладки, которые, на первый взгляд, могут сразу не бросаться в глаза, но которые образуют отдельную систему, представленную как в ядре, так и за его пределами.

- Систему шин, связывающих все компоненты МК в единую систему.

- Периферию МК, связанную с ядром системой шин.

Рассмотрим каждую из этих частей подробнее.

Ядро Cortex-M4F

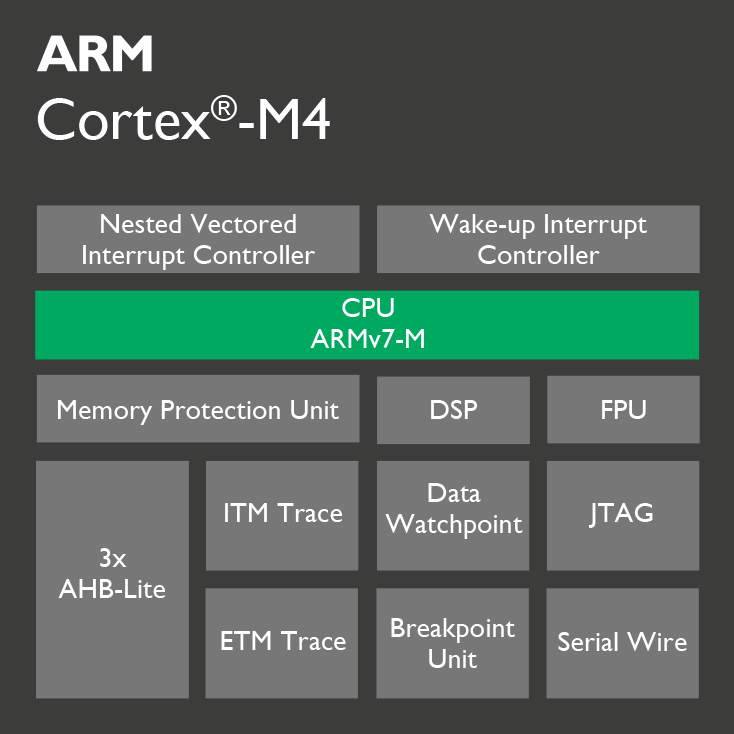

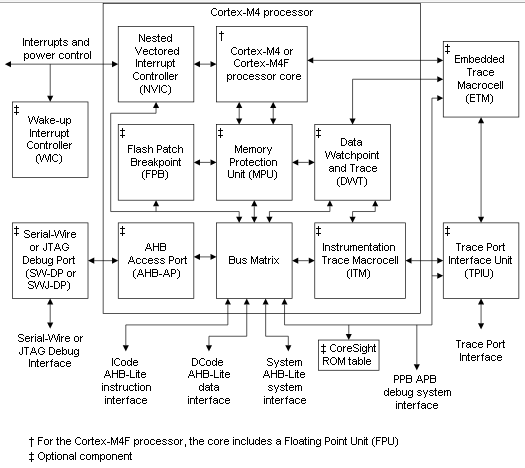

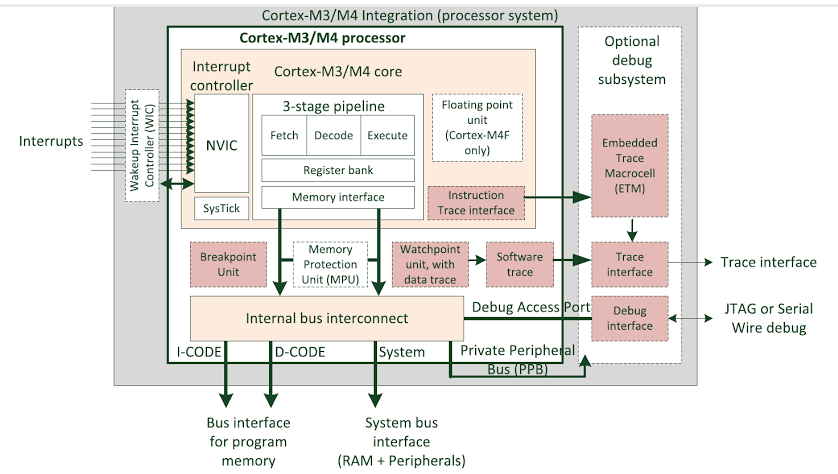

Рассматриваемые МК базируются на ядре Cortex-M4F — варианте ядра Cortex-M4, у которого, в добавление к базовому варианту, присутствует блок операций с плавающей запятой одинарной точности. Варианты изображения структурной диаграммы ядра показана на рис.2 — рис.5.

Концептуально ядро Cortex-M4F отличается от ядра Cortex-M3 поддержкой инструкций DSP и блоком операций с плавающей запятой, поэтому, литература и другие источники, описывающие ядро Cortex-M3 во многом подойдут и для понимания Cortex-M4F. На некоторых рисунках, приводимых ниже, можно так же увидеть подписи, обозначающие Cortex-M3, но информация справедлива и для Cortex-M4F.

Архитектура набора команд

Архитектура ARMv7E-M определяет тип архитектуры набора команд и отличается от базовой архитектуры ARMv7-M (ссылка на Reference Manual pdf), использованной в ядрах Cortex-M3, наличием дополнительного набора инструкций с насыщением и SIMD инструкций, представляющими DSP-расширение.

Сравнение ядер Cortex-M по поддерживаемым инструкциям можно увидеть на рис.6-7.

Ядра Cortex-M3/4 поддерживают набор инструкций Thumb-2. Традиционные процессоры ARM поддерживали два набора команд — ARM — 32-х битные команды, обеспечивающие более высокое быстродействие, но код с такими командами требовал и больше места, и Thumb — 16-ти битные команды, код требовал меньше места, но и быстродействие было меньше, так как и возможности таких команд более ограничены. Набор Thumb-2 включает смешанные 32-х и 16-ти битные инструкции, что даёт возможности достичь компромисс между быстродействием и плотностью кода. Набор Thumb, при этом, поддерживается, являясь подмножеством Thumb-2. На рис.6-7 32-х и 16-ти битные команды можно различать по длине скруглённых боксов, в которые вписаны их имена.

Более подробно наборы инструкций, их особенности и группы я планирую описать в отдельной заметке, посвящённой ассемблеру ARM применительно к Cortex-M4.

Центральное процессорное устройство

Центральное процессорное устройство (ЦПУ, CPU — Central Processing Unit), CM4Core, основан на ядре ARMv7-M реализованному по Гарвардской архитектуре. Но при этом, Гарвардская архитектура реализована не классических образом. Ядро имеет раздельные каналы для инструкций и данных, но инструкции и данные разделяют одно и тоже адресное пространство, и физически могут находится на одном устройстве памяти.

CPU включает интерфейсы контроллера вложенных векторизованных прерываний (КВВП, NVIC — Nested Vectored Interrupt Controller), шины инструкций, шины данных, отладки, логику управления, систему выборки, дешифрации и исполнения команд, Арифметико-логическое устройство (АЛУ, ALU — Arithmetic and Logic Unit), банк регистров.

В CPU реализован трёхступенчатый конвейер (Instruction Pipeline). Обработка каждой команды осуществляется в три этапа — выборка, декодирование, выполнение. Диаграмма работы конвейера показана на рис.8.

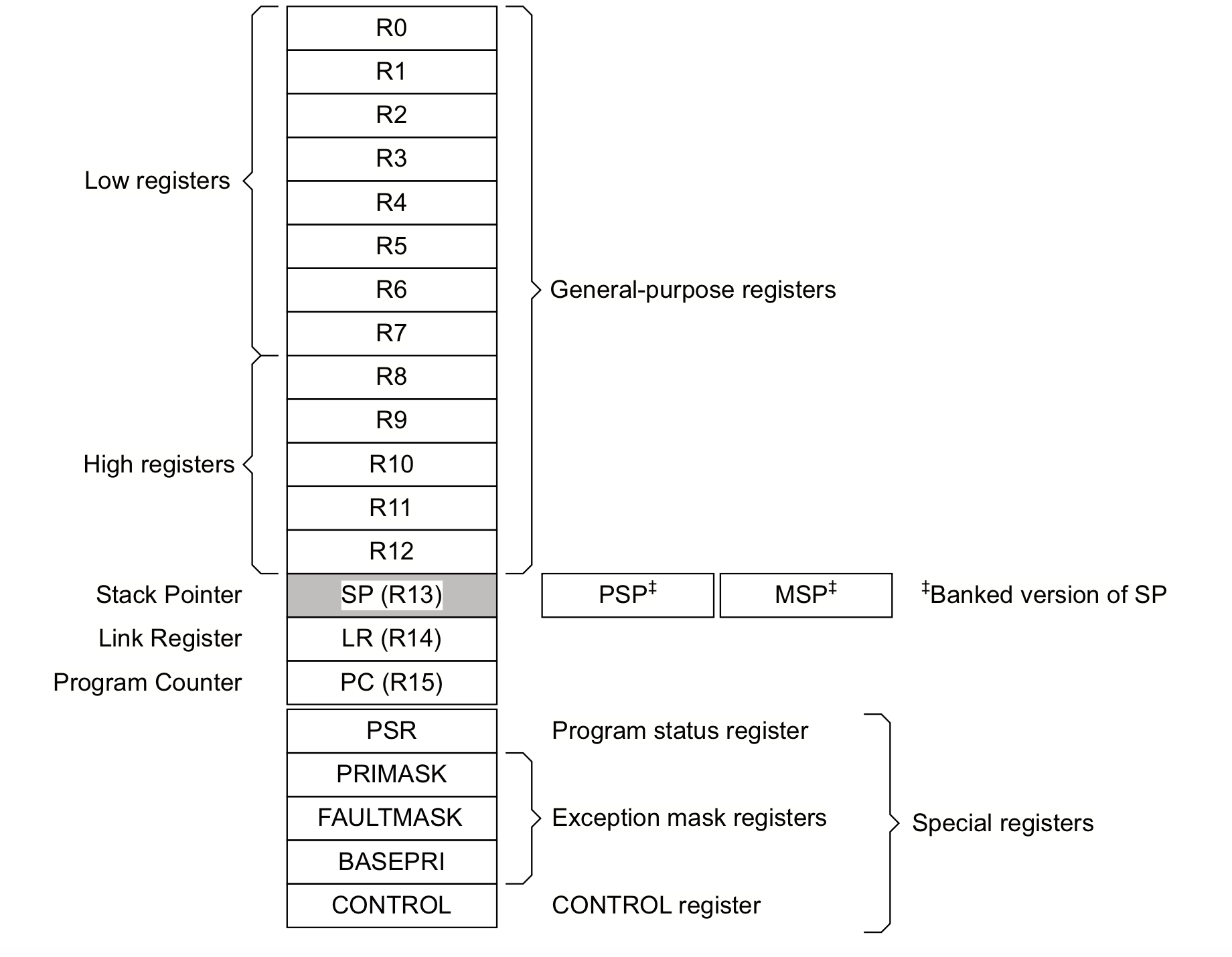

Программно доступные регистры CPU показаны на рис.9. Все регистры 32-х битные. Регистры описываются в разделе 2.1.3 ПР (Программистское Руководство, PM0214).

Регистры R0 — R12 представляют собой регистры общего назначения. Из них R0 — R7 — младшие регистры, R8 — R12 — старшие. Практическая разница между ними в том, что большинство 16-ти битных команд набора Thumb-2 могут иметь доступ только к младшим регистрам.

Регистр SP (R13) — Указатель стека (SP — Stack Pointer). Содержит два регистра, объединённые в банк. Ядро может работать в привилегированном и непривилегированном режиме доступа к коду, подобно режиму ядра операционной системы, и режиму прикладных программ.

- Основной указатель стека (MSP — Main Stack Pointer) — используется для работы в режиме ядра.

- Указатель стека процесса (PSP — Process Stack Pointer) — используется прикладными программами.

Два младших бита SP всегда сброшены в 0 для выравнивания на границу 32-битного слова, которое и является минимальной порцией данных, которая может быть помещена/извлечена в стек.

Читать/изменять значения для скрытого в данный момент регистра можно через инструкции доступа к специальным регистрам.

Регистр LR (R14) — Регистр связи (LR — Link register). Служит для запоминания адреса возврата при вызове подпрограммы.

Регистр PC (R15) — Счётчик команд (PC — Program Counter). Регистр, служащий в качестве счётчика выполняемых команд. Из-за наличия конвейера значение PC обычно равно адресу текущей выполняемой команды + 4. Запись значения в PC приводит к переходу по указанному адресу.

Здесь есть одна тонкость. Как отмечено выше, классические процессоры ARM поддерживали два набора команд — ARM и Thumb.

Так как инструкции могут быть либо 32-х либо 16-ти битными младший бит адреса команды всегда сброшен в 0. Но в процессорах ARM младший бит использован для определения режима работы — ARM или Thumb. Процессоры Cortex-M поддерживают Thumb-2, который по отношению к набору ARM тот же Thumb, то есть, для него младший бит, загружаемого в R15 значения, должен быть установлен в 1, иначе процессор попытается переключиться в режим ARM, а так как у ядер Cortex-M данный режим отсутствует, это вызовет переход на обработчик исключительной ситуации. Программируя на Си об этот задумываться не приходиться, однако, программируя на ассемблере, к меткам, используемым с командами, загружающими значение PC значением метки, а так же к меткам, используемым в таблице прерываний, необходимо прибавлять 1, либо использовать специальные директивы ассемблера. Подробнее об этом планируется в заметке о программировании на ассемблере, а так же соответствующих примерах.

Описываемые ниже регистры относятся к группе регистров специального назначения. Они не могут адресоваться непосредственно, как указанные выше, большинством команд. Для чтения/записи их значений используются инструкции MSR и MRS.

Регистр PSR (xPSR) — Регистр состояния программы (Program Status Register). Регистр представляет собой 3 регистра, к которым возможен доступ как по отдельности, так и как к единому регистру PSR.

- APSR (Application PSR) — Регистр состояния приложения.

- IPSR (Interrupt PSR) — Регистр состояния прерывания.

- EPSR (Execution PSR) — Регистр состояния выполнения.

Структурная схема регистра PSR приведена на рис.10.

Значения полей регистра PSR приведены в таблице 1.

| Поле | Имя | Описание |

|---|---|---|

| [31] | N | Отрицательное значение |

| [30] | Z | Нулевое значение |

| [29] | C | Перенос/заём |

| [28] | V | Переполнение |

| [27] | Q | Насыщение |

| [26:25], [15:10] | ICI/IT | Состояние команды, выполняемой после прерывания/состояние команды блока IF-THEN |

| [24] | T | Признак Thumb кода. Должен быть всегда выставлен в 1, иначе будет сгенерировано исключение. |

| [8:0] | ISR_Number | Номер прерывания, обрабатываемого в настоящий момент |

Состояние полей N, Z, C, V, Q определяется последней инструкцией, изменяющей значение данных флагов, в соответствии с условием в описании. Если описанное условие выполняется, соответствующий бит устанавливается в 1.

Поле ICI/IT предназначено для хранения состояния выполнения условного блока IT (подробнее планируется в заметке о программировании на ассемблере) или состояния выполнения операций групповой загрузки/сохранения LDM и STM.

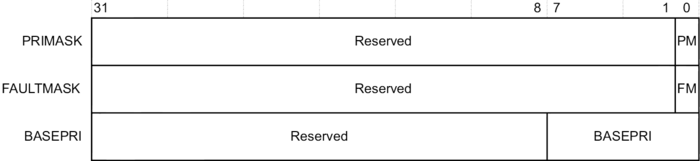

Регистры PRIMASK, FAULTMASK, BASEPRI образуют группу регистров маскирования прерываний и исключений.

Структурная схема регистров маскирования прерываний показана на рис.11.

Регистр PRIMASK — регистр основной маски прерываний (Priority Mask Register). Когда бит PM [0] установлен, приоритет выполняемого в данный момент кода становится равным 0. Код может быть прерван только прерыванием или исключением, имеющим меньшее значение приоритета (чем меньше значение приоритета — тем приоритет выше). В данном случае к таким относятся тяжёлый отказ (Hard Fault), немаскируемое прерывание (NMI — Non-Maskable Interrupt) и сброс. Подробнее о прерываниях и исключениях ниже в этой заметке.

Регистр FAULTMASK — регистр маски отказов (Fault Mask Register). Когда бит FM [0] установлен, приоритет выполняемого в данный момент кода становится равным -1. Он может быть прерван только NMI и сбросом. Установка бита FM возможна только при текущем уровне приоритета равным или большим 0. Попытки установить бит в обработчиках тяжёлого отказа или немаскируемого прерывания будут проигнорированы. При возврате из обработчика любого прерывания, кроме немаскируемого, бит FM сбрасывается.

Регистр BASEPRI — регистр базового приоритета (Base Priority Mask Register). Регистр имеет одноимённое поле BASEPRI [7:0]. Сброс поля в ноль не будет иметь эффекта. Установка же его в значение, отличное от 0, приведёт к тому, что процессор не будет обрабатывать любые прерывания и исключения со значением приоритета больше или равным, установленному в поле BASEPRI.

Регистр CONTROL — контрольный регистр. Имена и описания полей приведены в таблице 2.

| Поле | Имя | Описание |

|---|---|---|

| [2] | FPCA | Бит разрешения работы математического сопроцессора (FPU). Если 0, работа сопроцессора запрещена, если 1 — разрешена. |

| [1] | SPSEL | Бит выбора активного указателя стека. Если 0 — текущим указателем стека будет указатель основного стека (MSP). Если 1 — указатель стека процесса (PSP). При работе в режиме обработчика (См. ниже «Режимы работы») запись значения игнорируется, но будет применена после возвращения из обработчика. |

| [0] | nPRIV | Определяет привилегированность кода в режиме потока (См. ниже «Режимы работы»). 0 — код привилегированный, 1 — непривилегированный. |

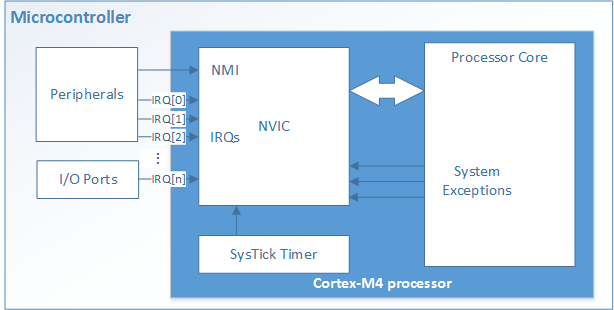

Контроллер вложенных векторизованных прерываний

Контроллер вложенных векторизованных прерываний (КВВП, NVIC — Nested Vectored Interrupt Controller) описан в разделе 4.3 ПР и параграфе 2.2.10 ДШ. Контроллер позволяет управлять работой системы прерываний МК. Понятие «вложенных» подразумевает, что при выполнении прерываний они могут прерываться другими прерываниями, имеющими более низкое значение уровня приоритета. Понятие «векторизованных» означает, что каждый тип прерывания имеет собственный вектор — адрес, по которому сразу же при возникновении прерывания будет передано управление. Другой способ обработки прерываний — невекторизованный, используется, например, в 8-ми битных МК PIC16. Там при возникновении всех прерываний происходит переход по адресу одного и того же обработчика, в котором проверяется, флаги какого прерывания установлены, и в зависимости от результатов проверки выполняются требуемые действия.

Более подробно описать его планируется в отдельной заметке о работе с прерываниями, здесь же перечислю только его основные характеристики.

- Возможность установки до 16 (0-15) уровней приоритета прерываний.

- Обработка до 82 маскируемых каналов прерываний плюс 16 линий прерываний ядра.

- Определение прерывающих сигналов по уровню и по фронту.

- Динамическое изменение приоритетов прерываний.

- Группировка прерываний по приоритету, а внутри групп по субприоритету.

- «Цепочная» обработка прерываний. Способ ускорения обработки прерываний, когда, в случае возникновения во время обработки прерывания, другого прерывания, со значением уровня приоритета, равным или большим обрабатываемого, после окончания обработки первого прерывания, переход ко второму будет производится без восстановления значения регистров из стека.

- Внешнее немаскируемое прерывание (NMI).

Диаграмма взаимодействия КВВП с другими компонентами МК показана на рис.12.

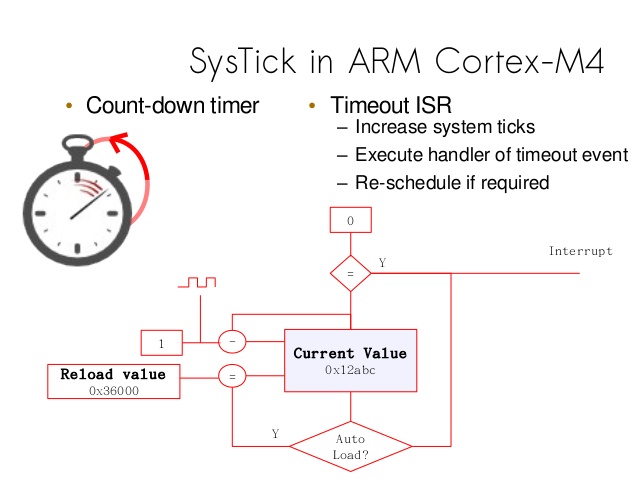

Системный таймер

Системный таймер SysTick — встроенный в ядро 24-х битный таймер обратного отсчёта, производящий декрементирующий отсчёт от заданного значения до 0. По достижении 0 происходит прерывание. Как видно на рис.12 SysTick таймер соединён с КВВП. Таймер описан в ПР р. 4.5. Он может использоваться для различных целей, требующих совершения периодических действий. Основное целевое назначение — системный таймер операционных систем. Диаграмма алгоритма работы SysTick таймера показана на рис.13.

Контроллер пробуждающих прерываний

Контроллер пробуждающих прерываний — (КПП, WIC — Wakeup Interrupt Controller) — модуль, связанный с контроллером прерываний NVIC, но отделённый от основной схемы процессора. Предназначен для пробуждения системы в тех случаях, когда процессор, включая NVIC, полностью отключён.

Для ядер Cortex-M4 данный модуль является опциональным. Я не нашёл его упоминаний, применительно к МК STM32. Но возможности, предоставляемые этим модулем у них присутствуют (пробуждение из режимов Stop и Standby по сигналам на внешних выводах МК и по прерыванию от часов RTC). Возможно, его упоминание посчитали не заслуживающим внимания, включив в состав логики пробуждения, но может быть, в МК STM32, для этих целей применено собственное решение. Как бы там ни было, но данный модуль какого-либо специального программирования не требует, и ведут себя рассматриваемые МК так, как если бы он присутствовал.

Модуль защиты памяти

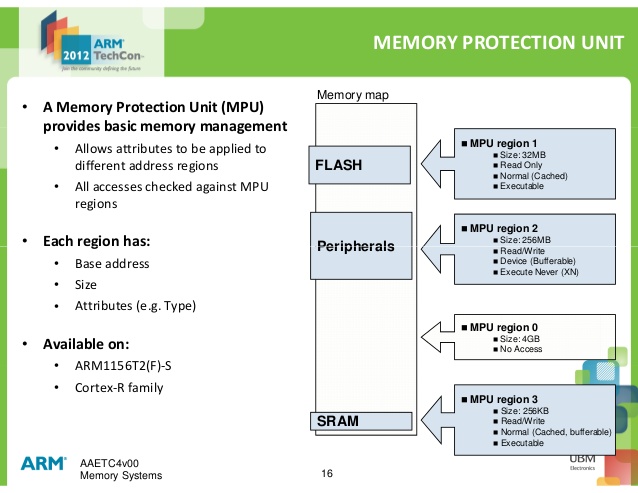

Модуль защиты памяти — (MPU — Memory Protection Unit) — предназначен для повышения надёжности системы, путём управления правами доступа к определённым регионам памяти. Данный модуль описан в разделе 4.2 ПР.

MPU позволяет делить карту памяти на регионы (до 8 регионов, возможны и подрегионы), определять для каждого региона локализацию, размер, права доступа и атрибуты памяти. При помощи MPU, можно, например, запретить непривилегированному коду изменять данные в областях системной памяти, или определить некоторые области оперативной памяти как неиспользуемые, для предотвращения возможности внедрения в них вредоносного кода.

На рисунке 14 приведена схема разбиения карты памяти на регионы. Схема относится к профилю Cortex-R, но, в общем, подходит и для Cortex-M4 с MPU, за исключением того, что указанные размеры и некоторые атрибуты могут быть неприменимы.

Цифровой сигнальный процессор

Цифровой сигнальный процессор — (Цифровой Процессор Обработки Сигналов — ЦПОС, Digital Signal Processor — DSP) — представляет расширение Центрального Процессорного Устройства — CPU, реализующее команды, специально нацеленные на ускорение обработки оцифрованных сигналов — арифметических операций с насыщением (когда, для беззнакового 8-ми битного числа будет 255+1=255), SIMD-инструкций (одна инструкция выполняется над множеством данных, см. рис.15), инструкций умножения-сложения (MAC).

Данный модуль может применяться для компрессии/декомпрессии сигналов, подавления шумов, сглаживания сигналов. Например, в системах обработки звука, передачи данных, управления двигателями.

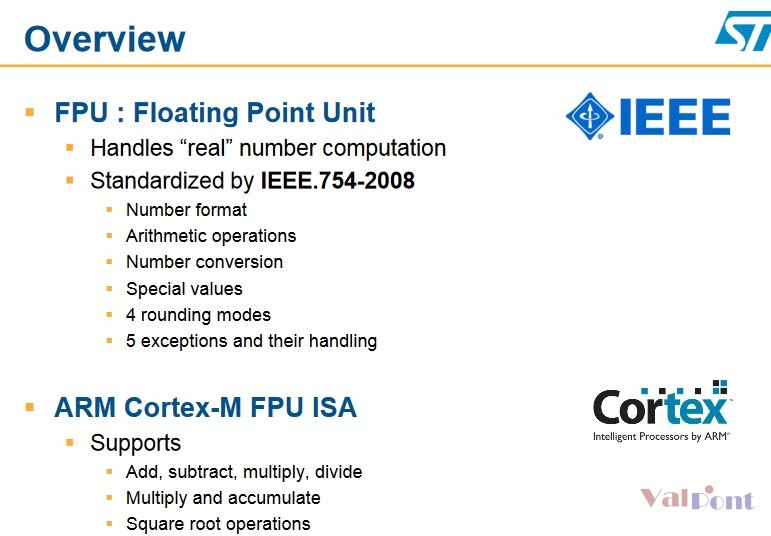

Математический сопроцессор

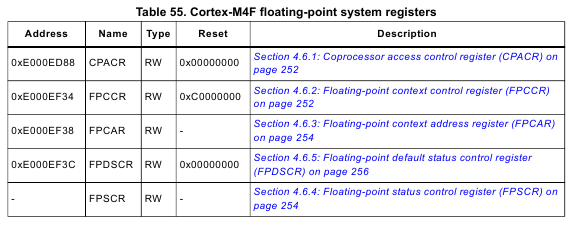

Математический сопроцессор — (FPU — Floating Point Unit) — модуль, предназначенный для осуществления операций с плавающей запятой. FPU Cortex-M4F реализует вычислительные операции одинарной точности — число занимает 32 бита. FPU описывается в разделе 4.6 ПР.

FPU имеет 5 системных регистров, и 32-а 32-х битных численных регистра, доступ к которым может осуществляться так же как к 16-ти 64-битным регистрам для операций загрузки, сохранения и перемещения, см. рис.17-18.

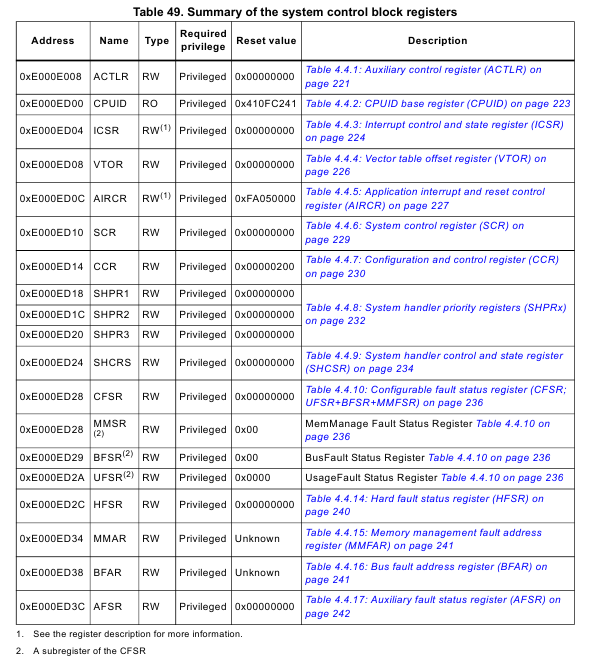

Системный контрольный блок

Системный контрольный блок — (SCB — System Control Block) — модуль, содержащий регистры, поддерживающие получение системной информации и осуществление системного контроля. Описан в разделе 4.4 ПР. С перечислением регистров блока и их именами можно ознакомиться на рис.19.

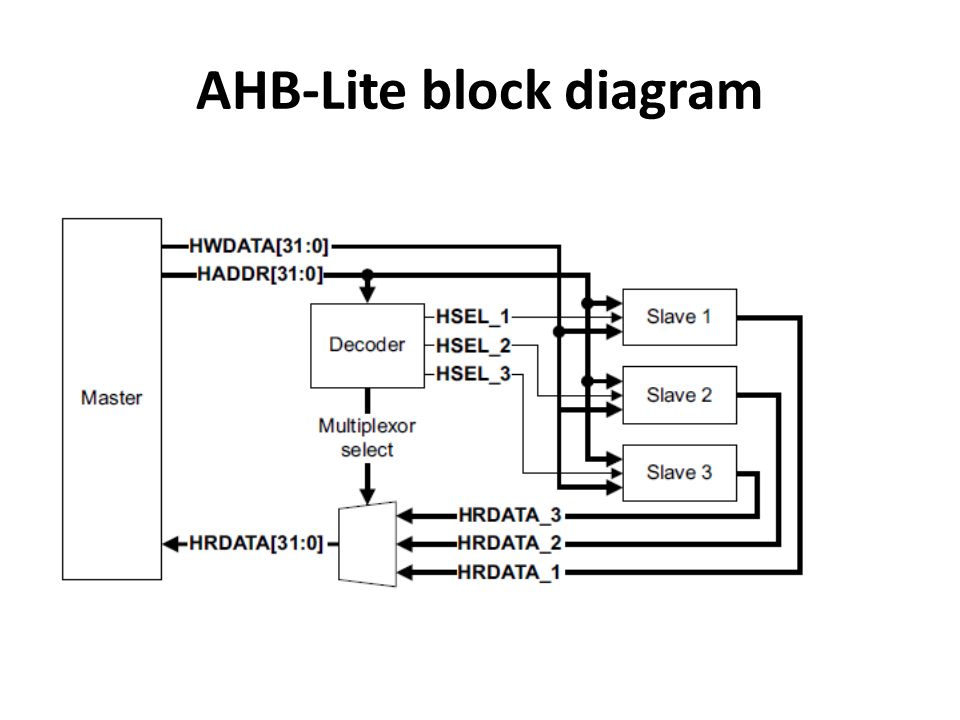

Матрица шин

Матрица шин — (Bus Matrix) — модуль внутрипроцессорной коммуникации шин, соединяющий компоненты ядра с внешними (по отношению к ядру) шинами. Не следует путать данный модуль, являющийся внутренним компонентом ядра Cortex-M4, с рассматриваемым далее модулем Multi-AHB matrix, который является внешним по отношению к ядру компонентом МК и служит для соединения ведущих (masters) и ведомых (slaves) (по принципу инициализации передачи данных) устройств МК, и к которому также подключены внешние шины, соединённые с рассматриваемым сейчас модулем ядра.

Внешние шины, соединяющие ядро с периферией МК, реализуют соответствующие варианты спецификации шинной архитектуры AMBA 3 (ARM Advanced Microcontroller Bus Architecture — Развитая Шинная Архитектура Микроконтроллера). Cortex-M4 предоставляет три первичных шинных интерфейса реализующих вариант протокола AMBA 3 AHB-Lite, являющегося урезанным вариантом AHB (Advanced High-performance Bus — Развитая Высокопроизводительная Шина), и один интерфейс для системы отладки, реализующий AMBA 3 APB (Advanced Peripheral Bus — Развитая Шина Периферии) протокол. Непосредственно знание спецификации данных шин не требуется для программирования или разработки устройств на МК, оно может потребоваться только при проектировании собственно микроконтроллеров или систем на кристалле.

Внешние шины, соединяющие ядро с периферией МК (первые три описаны в параграфах 2.1.1-2.1.3 СР), см. так же рис.20:

- Шина I-bus — шина инструкций, работает по протоколу AHB-Lite, служит для выборки команд из области памяти 0x00000000 — 0x1FFFFFFF (пространству кода, см. карту памяти ниже). Выборка производится 32-х разрядными словами, даже если инструкции 16-ти битные.

- Шина D-bus — шина данных, работает по протоколу AHB-Lite, служит для выборки данных из области памяти 0x00000000 — 0x1FFFFFFFа так же отладочного доступа к данному пространству.

- Шина S-bus — системная шина, работает по протоколу AHB-Lite, служит для получения инструкций, данных и отладочного доступа к областям памяти 0x20000000 — 0xDFFFFFFF и 0xE0100000 — 0xFFFFFFFF (пространствам статического ОЗУ, периферийных устройств, внешнего ОЗУ, внешних устройств, памяти, определяемой производителем МК).

- Шина PPB — Частная Периферийная Шина (Private Peripheral Bus), работает по протоколу APB, поддерживает доступ для данных и отладки к внутренним и внешним ресурсам процессора. Шина PPB делится на внутреннюю и внешнюю. Внутренняя соединяет внутренние модули ядра. Она осуществляет доступ к внутреннему пространству PPB 0xE0000000 — 0xE003FFFF. Собственно, APB PPB, является внешней. Подключается к матрице шин через мост AHB-APB. Она позволяет осуществлять доступ к региону 0xE0040000 — 0xE00FFFFF (внешнее пространство PPB), производители микросхем могут подключать к этой шине дополнительные устройства.

Так же матрица шин связана со следующими операциями:

- Конвертацией невыровненных пересылок в выровненные (выравнивание адреса на границу 32-х битного слова, два младшие бита адреса сброшены).

- Операциями бит-бэндинга (Bit Banding).

- Буферизацией записи — сохраняемые ядром данные записываются в буфер, и когда буфер становится полным, передаются по шине, пока буфер не опустеет. Это оптимизирует работу шин, предотвращая простои, связанные с ожиданием данных.

Идентификационные регистры

Архитектура ARMv7-M поддерживает набор регистров, значения которых позволяют получить информацию об особенностях архитектуры, реализованных для конкретного устройства. Подробности о данных регистрах можно прочитать в главе B4 ARM v7-M Architecture Reference Manual.

Данные регистры делятся на следующие группы:

- Идентификационные регистры особенностей процессора.

- Идентификационный регистр системы отладки.

- Вспомогательный идентификационный регистр.

- Идентификационные регистры особенностей памяти.

- Регистры атрибутов набора инструкций.

- Регистры особенностей математического сопроцессора и медийных инструкций (SIMD и т.п.).

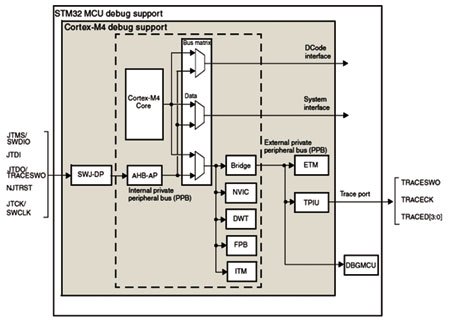

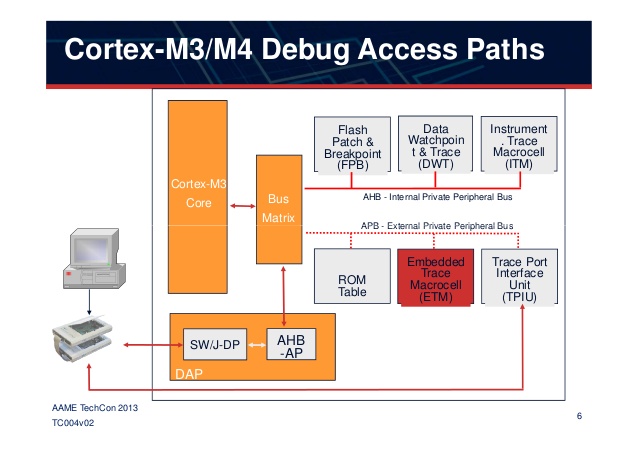

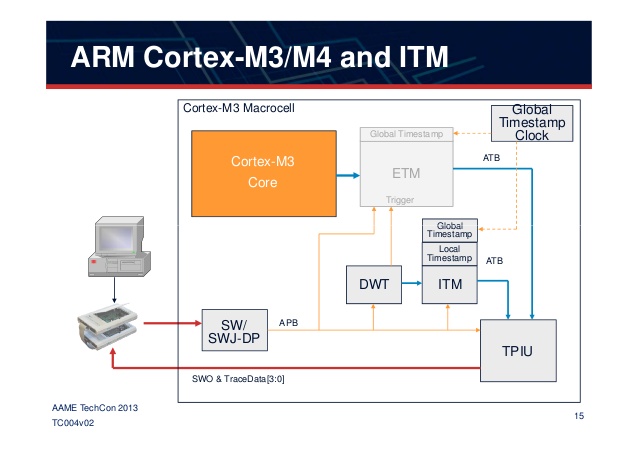

Система отладки

Система отладки представляет собой целостную структуру, включающую в себя ряд компонентов. Часть этих компонентов архитектурно входят в состав ядра Cortex-M4, другие, по отношению к нему, рассматриваются как внешние периферийные устройства. Функционально система отладки представляет собой отдельную систему, достаточно независимую от основной вычислительной системы, что позволяет минимизировать влияние процесса отладки на выполнение программы.

Система отладки описывается в разделе 38 СР. Она представляет подмножество системы отладки ARM CoreSight.

Описания в СР дают только общее представление о системе. Этого описания достаточно для представления о возможностях, предоставляемых отладочной системой для целей прикладного программирования, но для целей разработки программного обеспечения, предназначенного для поддержки возможностей отладки (отладчиков и т.п), его может оказаться недостаточным. Ссылки на документы, более подробно описывающие архитектуру отладки, приводятся в подразделе 38.2 СР.

Система отладки поддерживает следующие возможности:

- Поддержка отладки по протоколам JTAG и Serial Wire

- Возможности отладки ядра: останов, одиночный шаг, возобновление, сброс, доступ к регистрам.

- Доступ к памяти и регистрам периферии во время исполнения кода.

- Шесть аппаратных точек останова на доступ к инструкциям и две на доступ к данным.

- Неограниченное число программных точек останова.

- До 4 компараторов аппаратных точек наблюдения.

- Трассировка инструкций.

- Трассировка данных.

- Программная трассировка.

- Отбор значений программного счётчика (PC)

- Логика подмены значений flash-памяти.

Ядра Cortex-M3/M4 предусматривают два режима отладочных операций. Первый — режим останова — выполнение всех операций процессором приостанавливается. Второй — режим исключения Debug Monitor — процессор продолжает работать, отлаживаемая ситуация обрабатывается в обработчике отладочного исключения. Исключения с приоритетом выше отладочного могут при этом происходить. Данный режим необходим для отладки устройств, для которых полная остановка процессора может привести к повреждению управляемого ими оборудования.

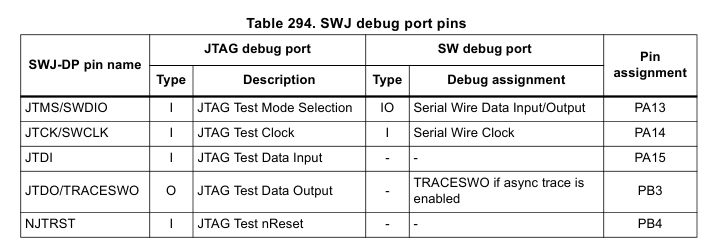

Порт отладки SWJ-DP

Порт отладки SWJ-DP — комбинированный порт отладки Serial Wire/JTAG (Serial Wire/JTAG-debug port). Система CoreSight проектировалась с учётом возможности подключения к внешним устройствам отладки (персональный компьютер, например) с использованием различных интерфейсов. Устройства на основе ядер Cortex-M4 могут использовать для подключения устройства к отлаживающему компьютеру интерфейсы JTAG (5 сигнальных линий) и Serial Wire (2 сигнальных линии). Данные интерфейсы описаны в подрезделах 38.7-38.8 СР соответственно.

В МК STM32F407 реализован совмещённый интерфейс Serial Wire/JTAG, который специальными последовательностями команд может переключаться для работы по любому из этих протоколов. Он описан в 38.3 СР и 2.2.38 ДШ.

Порт доступа AHB-AP

Порт доступа AHB-AP (AHB access port) является ведущим AHB устройством, осуществляющим связь между SWJ-DP отладочным портом и матрицей шин. Модуль обеспечивает доступ ко всей памяти процессора используя несколько регистров. Модуль управляется модулем SWJ-DP через порт доступа к средствам отладки (DAP — Debug Access Port). Описан в подразделе 38.9 СР.

Таблица ПЗУ

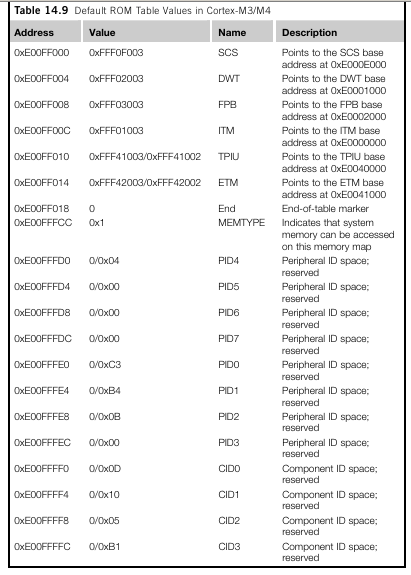

Таблица ПЗУ (ROM table) используется для автоматического обнаружения отладчиком компонентов отладки. Таблица содержит сведения о расположении в памяти системных компонентов и компонентов отладки. Компоненты отладки имеют идентификаторы, позволяющие определить их присутствие в системе, а так же идентификаторы, определяющие особенности их реализации. Содержание таблицы ПЗУ по умолчанию показано на рис.31. На рис.32 показана схема автоматического определения компонентов отладки и их возможностей отладчиком.

Два младших бита значения в таблице ПЗУ определяют наличие компонента. Если они оба установлены, значить компонент присутствует. Остальные биты определяют смещение начала регистров компонента в памяти от стартового адреса таблицы ПЗУ. То есть, для получения адреса компонента надо к стартовому адресу таблицы ПЗУ (0xE00FF000) прибавить значение для компонента из таблицы, сбросив младшие два бита, и округлить получившийся результат до 32 бит.

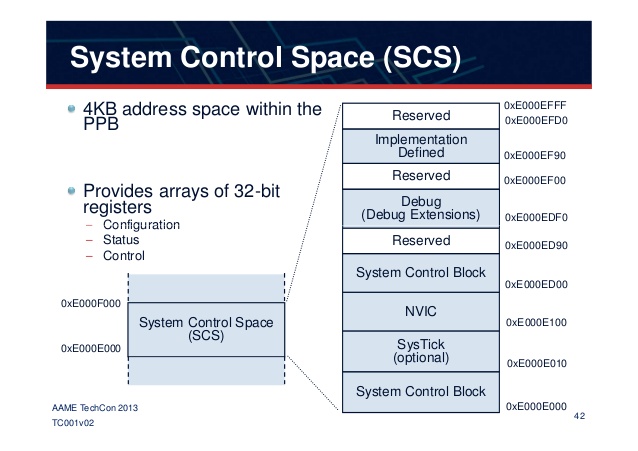

Отладочные регистры в системном контрольном пространстве

Отладочные регистры в системном контрольном пространстве — (SCS — System Control Space, см. рис.33) включают в себя два относящиеся к отладке регистра в Системном Контрольном Блоке (SCB) и группу регистров в Отладочном Контрольном Блоке (DCB — Debug Control Block).

В SCB к системе отладки относятся регистры ICSR (Interrupt Control and State Register) — точнее, его флаги ISRPREEMPT и ISRPENDING — и DFSR (Debug Fault Status Register).

Регистры DCB описаны в подразделе 38.10 СР. Краткое их описание приводится так же ниже, в таблице 3. Эти регистры не сбрасываются системным сбросом, они сбрасываются только сбросом по подаче питания.

| Регистр | Описание |

|---|---|

| DHCSR | Debug Halting Control and Status Register — Отладочный регистр контроля останова и получения статуся. Поддерживает получение информации и осуществление управлением отладкой в режиме останова и шаговым выполнением команд |

| DCRCR | Debug Core Register Selector Register — Отладочный регистр выбора регистров. Поддерживает выбор процессорных регистров для передачи/получения данных. |

| DCRDR | Debug Core Register Data Register — Отладочный регистр данных регистра. Содержит данные прочитанные/записываемые из/в регистр процессора, определённый DCRCR. |

| DEMCR | Debug Exception and Monitor Control Register — Отладочный регистр отладочный исключений и мониторного контроля. Поддерживает управление отладочным исключением. |

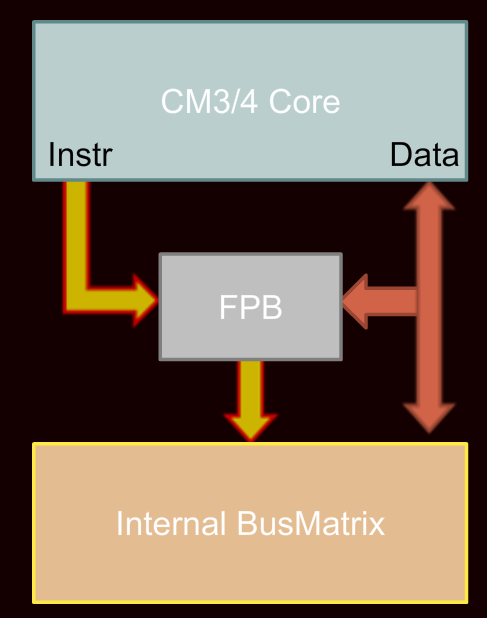

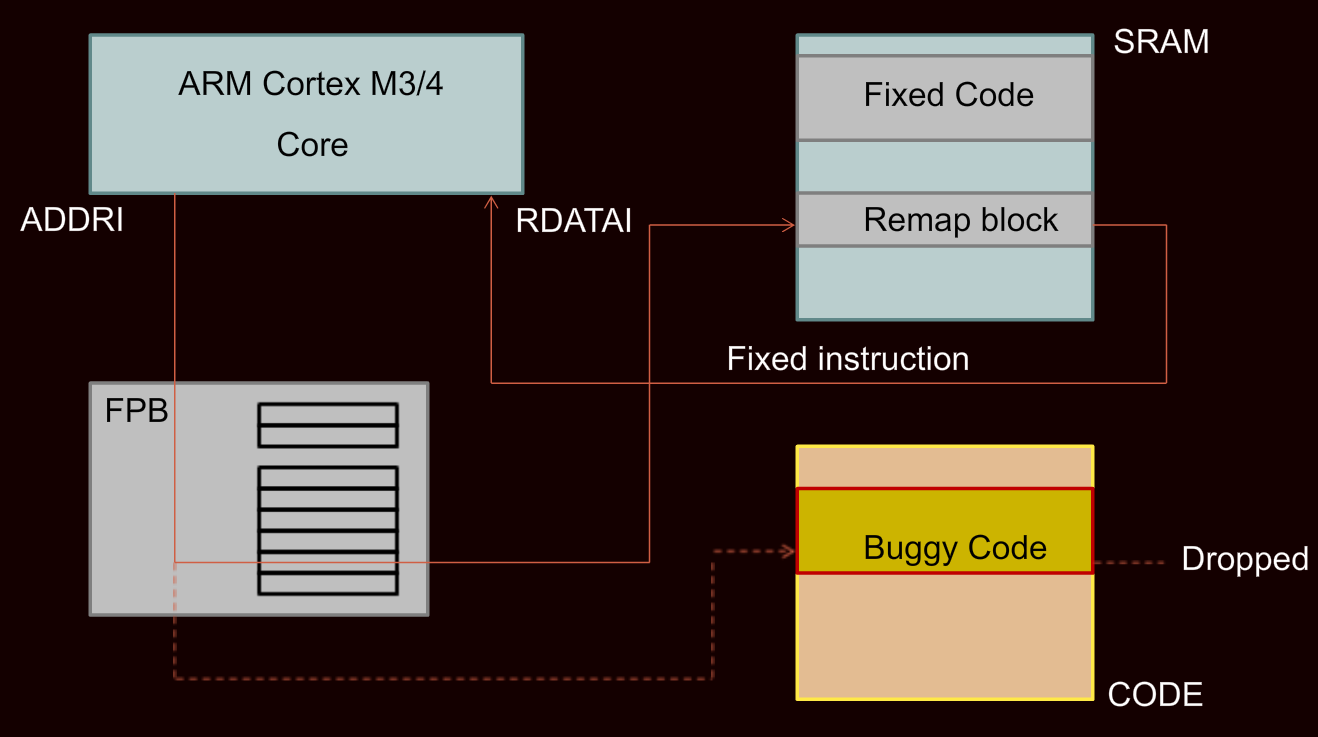

Модуль точек останова и подмены

Модуль точек останова и подмены — FPB (Flash Patch and Breakpoint Unit) — поддерживает установку аппаратных точек останова и подмену инструкций и данных. Описан в подразделе 38.12 СР. Содержит два компаратора для констант и шесть компараторов для инструкций. В случае совпадения адресов получаемых констант или инструкций из пространства кода со сравниваемыми, они могут быть подменены инструкциями или константами из системного пространства или произведена остановка процессора.

Функции подмены могут использоваться для установки заплаток на содержащую ошибки прошивку. Эта возможность актуальна для прошивок использующих однократно программируемую память, для перепрограммируемой она не актуальна.

Модуль точек наблюдения и трассировки данных

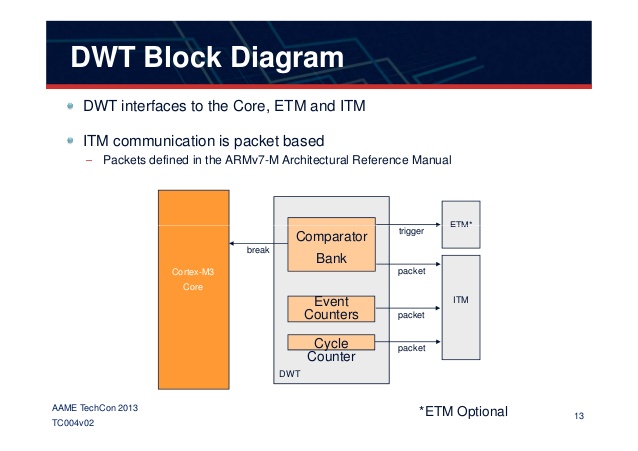

Модуль точек наблюдения и трассировки данных — DWT (Data Watchpoint and Trace Unit, Data Watchpoint Trigger) — модуль, поддерживающий аппаратные точки наблюдения, трассировку данных и системное профилирование. Описан в разделе 38.13 СР.

Трассировочная информация передаётся между компонентами отладки в виде пакетов, определённых в спецификации ARMv7-M архитектуры. Пакеты передаются по шине ATB (Advanced Trace Bus — Развитая Шина Трассировки).

Модуль имеет четыре компаратора, каждый из которых может быть настроен как:

- Аппаратная точка наблюдения — генерирует события наблюдения, переводящие процессор в один из режимов отладки.

- Триггер ETM — модуль ETM вставляет в поток трассировки команд триггер-пакет.

- Триггер события выборки счётчика команд (PC sampler).

- Триггер события выборки адреса (data address sampler).

DWT так же имеет счётчики, поддерживающие предоставление профилирующей информации:

- Числа тактов.

- Числа «свёрнутых» инструкций (folded instructions) — инструкций, выполнение которых занимает ноль тактов, такими могут оказаться инструкции барьерной синхронизации — DMB, DSB.

- Числа элементов операций загрузки/сохранения (LSU — Load store unit).

- Числа тактов, затраченных на выполнение инструкции (CPI — clock per instructions).

- Числа тактов, связанных с расходами на исключение (Interrupt overhead).

Инструментальная макроячейка трассировки

Инструментальная макроячейка трассировки — ITM (Instrumentation Trace Macrocell Unit) — управляемый приложением источник трассировки, который поддерживает вывод отладочной информации в стиле функции printf() для трассировки событий операционной системы и приложений и генерацию диагностической системной информации. Модуль имеет 32 порта стимулов, в которые различные процессы могут выводит отладочную информацию. Выводимые сообщения могут быть считаны через интерфейс порта трассировки или через интерфейс SWV (Serial Wire Viewer) модуля TPIU (см. ниже). Выведение данных через ITM напоминает вывод отладочных сообщений через UART, но так как вывод осуществляется через отдельную систему, это не вносит существенных задержек в работу программы. Модуль описан в подразделе 38.14 СР.

Модуль ITM имеет следующие возможности:

- Программная трассировка. Программа может напрямую записывать информацию в регистры стимулов ITM для генерации выводимых пакетов.

- Аппаратная трассировка. Модуль DWT генерирует пакеты, а ITM выводит их.

- Модуль ITM может вставлять временные метки (Timestamps) в поток трассировочных данных, помогая отладчику вести хронометраж трассировки. Для этих целей модуль имеет 21 битный счётчик.

- Глобальные системные временные метки. Временные метки могут опционально генерироваться с использованием системного 48-ми битного счётчика.

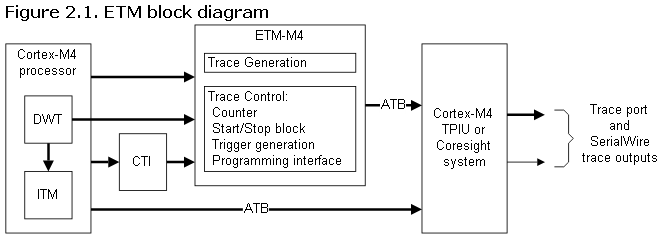

Встроенная макроячейка трассировки

Встроенная макроячейка трассировки — ETM (Embedded Trace Macrocell) генерирует пакеты трассировки команд, которые предоставляют возможность отладчику реконструировать выполнение программы. Модуль описан в подразделе 38.15 СР и более кратко в 2.2.39 ДШ.

Пакеты, генерируемые модулем, могут выводиться через порт TPIU. Для сокращения объёма передаваемых данных модуль может передавать информацию только о узловых точках (например, ветвления), по которым хостовый анализатор трассировки может восстановить ход выполнения программы.

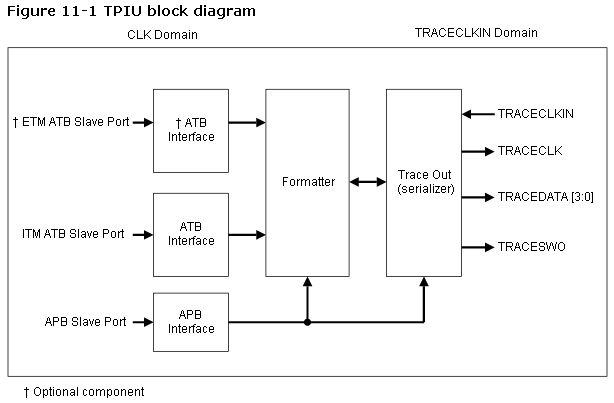

Интерфейс порта трассировки

Интерфейс порта трассировки — TPIU (Trace Port Interface Unit) — модуль, действующий как мост, соединяющий поток трассировочных данных из модулей ITM и ETM с внешним устройством, например, анализатором порта трассировки (TPA — Trace Port Analyzer). Модуль описан в подразделе 38.17 СР.

Модуль поддерживает два режима вывода информации: синхронный и асинхронный. В синхронном используется параллельная шина данных, разрядностью до 4-х бит. В асинхронном, иначе называемом SWV режиме, используется однопроводный интерфейс SWV (Serial Wire Viewer). Интерфейс может быть объединён с SWJ-DP, задействуя в SWD режиме линию JTAG TDO, которая при этом действует как третья линия SWD — Serial Wire Output (SWO). В МК STM32F40xxx реализована именно эта возможность. Так же эти МК, начиная со 100 выводного корпуса имеют и 4-х битную параллельную шину рассматриваемого интерфейса.

Отладочный компонент микроконтроллера

Отладочный компонент микроконтроллера — MCU Debug Component (DBGMCU) предоставляет поддержку для следующих возможностей отладки:

- Отладки в режимах пониженного энергопотребления.

- Контроля тактов для таймеров, сторожевого таймера, шин I2C и bxCAN во время точек останова.

- Контроля назначения трассировочных пинов.

Описан в подразделе 38.16 СР.