В этой заметке продолжается рассмотрение внутреннего устройства МК серии STM32F407. Как ясно из нижеследующего заголовка, речь пойдёт о системных шинах микроконтроллера, статической оперативной и встроенной постоянной флэш памяти, а так же об интерфейсе встроенной флэш памяти с системными шинами.

Система шин и система памяти

Содержание

- Система шин МК

- Система памяти

- Шину кода I-bus

- Шину данных D-bus

- Системную шину S-bus

- Шину памяти DMA1

- Шину памяти DMA2

- Шину периферии DMA2

- Шину Ethernet DMA

- Шину USB OTG HS DMA

- Внутреннюю шину флэш-памяти ICode

- Внутреннюю шину флэш-памяти DCode

- Шину основной внутренней памяти SRAM1 (112 kB)

- Шину вспомогательной внутренней памяти SRAM2 (16 kB)

- Шину периферии AHB1, с подключёнными к ней AHB/APB мостами и APB периферией

- Шину периферии AHB2

- Шину контроллера внешней памяти FSMC — AHB3

- Основная внутренняя память SRAM1 (112 кБ)

- Вспомогательная внутренняя память SRAM2 (16 кБ)

- CCM (core coupled memory) — связанная с ядром память (64 кБ)

- Ёмкость 1 Мб

- Гарантированное число циклов программирования/очистки на сектор — 10000

- Размер читаемого блока данных — 128 бит

- Размер записываемых данных — байт, полуслово, слово, двойное слово

- Возможность полной и посекторной очистки

-

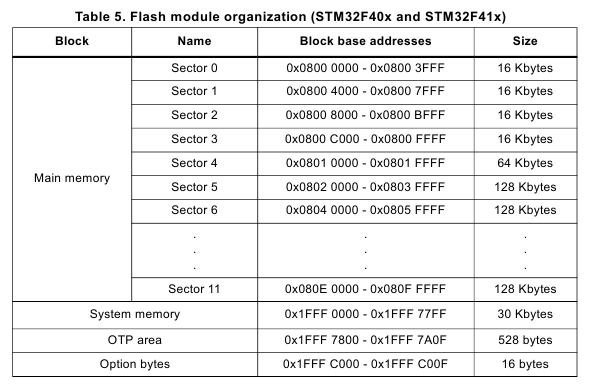

Организация:

- Основной блок памяти, служащий для сохранения программного кода и данных, в области программного кода, разделён на 4 сектора по 16 Кб, 1 сектор 64 Кб, 7 секторов 128 Кб.

- Системная память, содержащая загрузчик, исполняемый при загрузке в системном загрузочном режиме — 30 Кб. Не может быть перепрограммирована.

- Однократно программируемая память (OTP — one time programmable) для сохранения пользовательских данных — 512 байт. Данная память может перепрограммироваться до тех пор, пока в связанные с ней дополнительные 16 байт не установлены блокировочные значения, запрещающие перепрограммирование соответствующих байтам блоков OTP.

- Опциональные конфигурационные байты, определяющие защиту от чтения/записи флэш, уровень сброса по падению напряжения (BOR — Brown Out Reset), аппаратное/программное включение сторожевого таймера, сброс при переходе в STANDBY и STOP режимы — 16 байт

- Поддержка режимов пониженного энергопотребления

- Операции чтения флэш-памяти

- Операции программирования/очистки

- Защита от чтения/записи

- Предвыборка для шины I-Code

- 64 128-ми битные кэш линии для шины I-Code

- 8 128-ми битных кэш линий для шины D-Code

Система шин МК

Шинная архитектура описана в подразделе 2.1 СР.

Следует учитывать, что после сброса, тактирование всех подключённых к шинам периферийных устройств, кроме интерфейсов SRAM и флэш памяти, запрещено. Для перевода устройств в рабочее состояние, необходимо разрешить тактирование устройств через регистры контроля сброса и тактирования (RCC), относящиеся к той шине, к которой устройство подключено.

Многоуровневая матрица шин AHB

Многоуровневая матрица шин AHB — Multi-AHB bus matrix, соединяет ведущие и ведомые устройства, выступая в роли арбитра, предоставляющего доступ ведущим устройствам к ведомым. В качестве алгоритма предоставления доступа используется алгоритм карусели (Round-robin)

В МК STM32F407 матрица шин соединяет:

Восемь шин ведущих устройств:

Семь шин ведомых устройств:

Максимальная частота тактирования соединённых с матрицей шин AHB — 168 МГц.

Рисунок 41. Система шин MK STM32F407xx. (из Reference Manual RM0090)

Рисунок 42. Диаграмма соединения нескольких ведущих с несколькими ведомыми AHB-Lite через соединительную матрицу. (Взят с http://www.eetimes.com/document.asp?doc_id=1204405) Шины I-bus, D-bus, S-bus

Данные шины соединяют внутреннюю матрицу шин ядра Cortex-M4F c многоуровневой матрицей шин AHB микроконтроллера. Шины описаны выше в описании внутренней матрицы шин ядра.

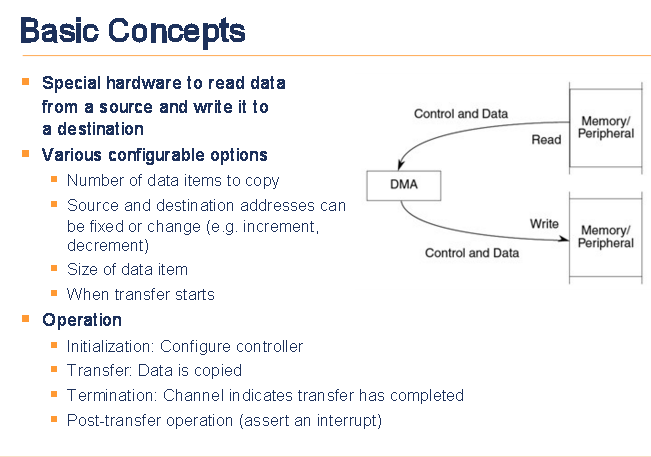

Шины памяти DMA

Шины памяти DMA соединяют интерфейсы шин памяти контроллеров Прямого Доступа к Памяти с многоуровневой матрицей шин. Они используются для передачи данных в/из памяти минуя CPU. Целевыми устройствами этих шин является память данных — внутренняя SRAM память (SRAM1, SRAM2), или внешняя память через FSMC.

Рисунок 43. Базовые концепции DMA. (Взят с http://slideplayer.com/slide/8010663/) Шины периферии DMA

Шины периферии DMA соединяют интерфейсы шин периферии контроллеров Прямого Доступа к Памяти с многоуровневой матрицей шин. Они используются контроллерами DMA для доступа к периферии или выполнения пересылок данных память-память. Целевыми устройствами этих шин являются AHB и APB периферия и память даных — внутренняя SRAM память (SRAM1, SRAM2), или внешняя память через FSMC.

Шина Ethernet DMA

Шина Ethernet DMA соединяет контроллер Ethernet DMA с многоуровневой матрицей шин. Шина используется контроллером Ethernet DMA для загрузки/сохранения данных памяти. Целевыми устройствами этой шины является память данных — внутренняя SRAM память (SRAM1, SRAM2), внутренняя флэш память или внешняя память через FSMC.

Шина USB OTG HS DMA

Шина USB OTG HS DMA соединяет контроллер USB OTG HS DMA с многоуровневой матрицей шин. Шина используется контроллером USB OTG HS DMA для загрузки/сохранения данных памяти. Целевыми устройствами этой шины является память данных — внутренняя SRAM память (SRAM1, SRAM2), внутренняя флэш память или внешняя память через FSMC.

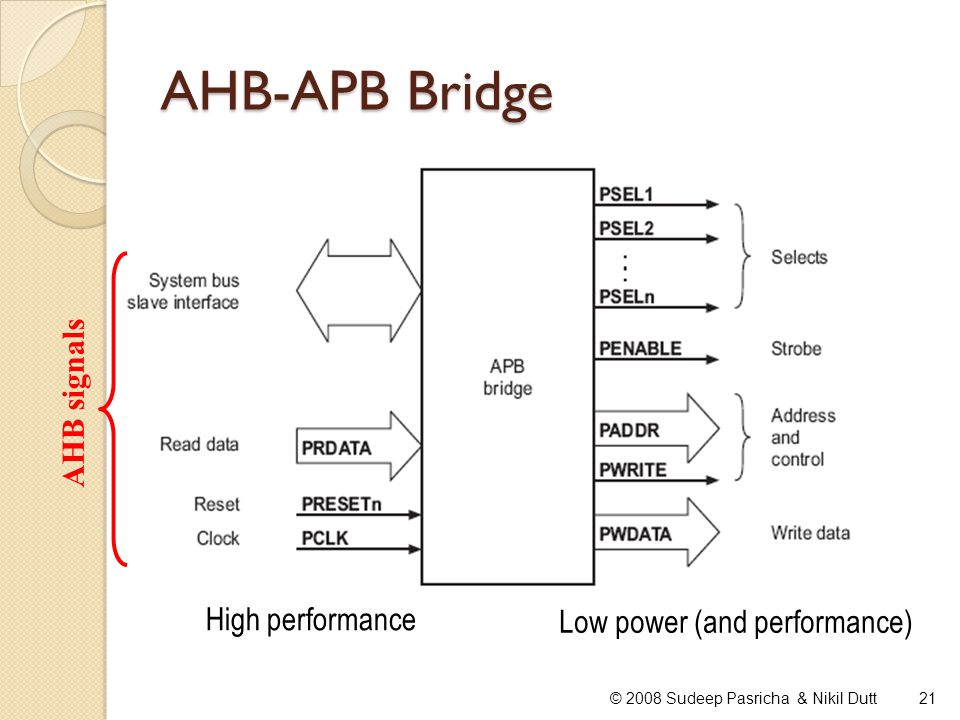

AHB/APB мосты

AHB/APB мосты (AHB/APB bridge) поддерживают полностью синхронное соединение между шиной AHB1 и соединёнными с ней шинами APB1 и APB2, позволяя осуществлять гибкий выбор частоты периферии.

Рисунок 44. Мост AHB-APB. (Взят с http://slideplayer.com/slide/1508721/) Шины APB

МК STM32F407 имеют две шины APB: низкоскоростную шину APB1 и высокоскоростную шину APB2. Максимальная частота тактирования APB1 — 42 МГц, APB2 — 84 МГц.

Система памяти

Встроенное статическое ОЗУ

Встроенное статическое ОЗУ — SRAM (Static Random Access Memory — Статическая память с произвольным доступом) МК STM32F407 включает в себя 196 кБ системного SRAM и 4 кБ резервной SRAM (backup SRAM) — энергозависимой памяти, с возможностью питания от батарейки, куда могут сохраняться данные с пользовательскими настройками работающего на МК ПО и прочая изменяемая информация, которая должна сохраняться после выключения питания и сбросов. Встроенная SRAM описана в 2.3.1 СР.

В свою очередь, системная SRAM делиться на:

SRAM1 и SRAM2 представляют собой единый регион, начинающийся с адреса 0x20000000. Различие проявляется в том, что SRAM1 может быть спроецирована на пространство кода, начинающееся с адреса 0x00000000. Тогда с этой памяти будет начинаться выполнение кода. См. режимы загрузки ниже.

К памяти SRAM1 и SRAM2 могут иметь доступ ведущие устройства DMA. CPU может иметь к ней доступ через S-bus. Или, когда загрузка происходит из SRAM1, он может обращаться к ней по I-bus и D-bus.

Память CCM начинается с адреса 0x10000000 и доступна только CPU по D-bus.

Рисунок 45. Ячейка SRAM. (Взят с http://helloworld2016.tistory.com/28) Встроенная Флеш-память

Встроенная Флеш-память — электрически стираемая перепрограммируемая энергонезависимая память (EEPROM — Electrically Erasable Programmable Read-Only Memory) предназначена для постоянного (независимого от состояния электропитания, сохроняемого после сбросов) хранения программного кода и данных. Описана в 2.3.2 и 3.3 СР. Дополнительные сведения о встроенной Флэш-памяти и работе с ней можно получить из AN3969.

Основные особенности Флэш-памяти МК STM32F407:

Рисунок 46. Организация Флэш-памяти MK STM32F407. (из Reference Manual RM0090) Интерфейс встроенной Флеш-памяти

Интерфейс встроенной Флеш-памяти управляет доступом шин I-Code и D-Code к флэш-памяти. Он реализует операции программирования и очистки, а так же операции защиты флэш-памяти от чтения и записи. Описан в разделе 3 СР.

Основные особенности:

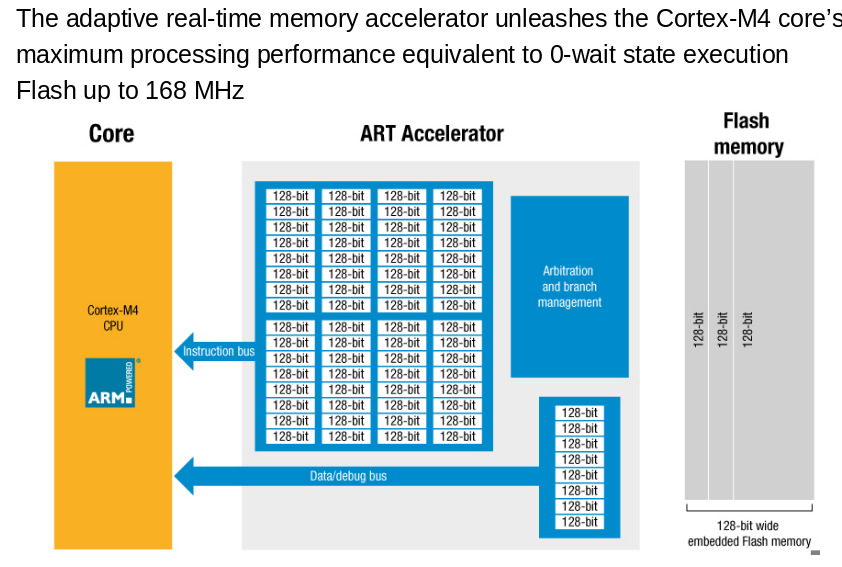

Рисунок 47. Соединения интерфейса Флэш-памяти внутри системной архитектуры. (из Reference Manual RM0090) Интерфейс Флэш-памяти включает в себя Адаптивный ускоритель памяти реального времени (ART Accelerator — Adaptive Real-Time Memory Accelerator) — описан в 3.5.2 СР. Акселератор предназначен для ускорения операций чтения Флэш-памяти. Он реализует кэширование читаемых из флэш-памяти данных и очередь предвыборки. Принцип работы основан на сохранении в статическом ОЗУ 128-ми битных порций читаемых из Флэш-памяти, что позволяет процессору получить к ним более быстрый доступ, так как операции обращения к статическому ОЗУ быстрее, чем к Флэш-памяти.

Рисунок 48. Принцип работы ART-акселератора. (Взят с http://electronicdesign.com/microcontrollers/cortex-m4-delivers-210-dmips-using-0-wait-memory) Обзор архитектуры и особенностей МК STM32F407 и ядра Cortex®-M4F — Часть I